Everywhere you look, computation is hiding in plain sight. It’s in the thermostat that anticipates your schedule, the inverter that squeezes more miles from an EV battery, the pump that doses a lifesaving drug, and the drone that avoids a tree at the last second. The brains behind these feats are embedded processors and controllers—specialized microchips engineered to run dedicated tasks with ruthless efficiency and reliability. This guide distills what they are, how they evolved, the major types you’ll encounter, and how to design real systems around them—plus where the field is headed next.

What Exactly Are Embedded Processors and Controllers?

Embedded processors are microprocessors tailored for control-centric workloads. They fetch and execute instructions, process inputs, and drive outputs—often inside a larger product rather than a general-purpose computer.

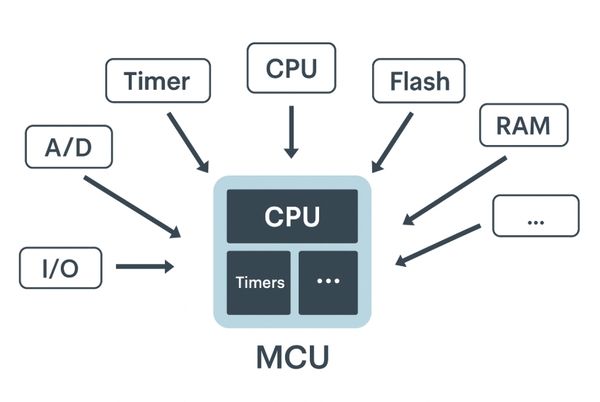

Embedded controllers, typically microcontroller units (MCUs), integrate a CPU plus nonvolatile program memory, RAM, timers, ADC/DAC, serial interfaces, and GPIO on a single die.

Together they form the core of an embedded system: a self-contained computing environment with tight constraints on power, latency, memory, and cost. Unlike PC CPUs, which optimize for throughput across many apps, embedded parts optimize for determinism, real-time behavior, and predictable resource usage. Their job is not to “run everything,” but to run one thing brilliantly, forever, and often in harsh environments.

- Mission-critical control: braking systems, flight computers, insulin pumps

- Latency-sensitive loops: motor control, power conversion, sensor fusion

- Resource-constrained designs: wearables, remote sensors, battery devices

A Brief Evolution: From 4-bit Curiosity to AI at the Edge

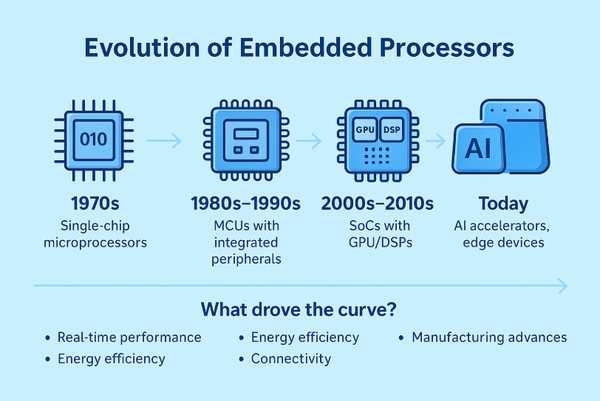

1970s: Single-chip microprocessors like the Intel 4004 prove the concept. Embedded control shifts from discrete logic to software-defined behavior.

1980s–1990s: Affordable MCUs (8/16-bit) marry CPU, memory, and I/O on one chip. Consumer appliances and automotive ECUs explode in capability.

2000s–2010s: 32-bit MCUs become mainstream; SoCs integrate DSPs, GPUs, radios, and robust security. RTOS options mature.

Today: Multicore MCUs, heterogeneous SoCs, AI/ML accelerators, and ultra-low-power designs enable edge inference, always-on sensing, and secure connectivity—all within tight power envelopes.

What pushed this curve? Growing demands for real-time performance, energy efficiency, and ubiquitous connectivity—plus manufacturing advances that deliver more capability per milliwatt and per dollar.

The Main Families You’ll Meet

1) Microcontrollers (MCUs)

Microcontrollers are the quiet specialists of electronics: compact, single-chip computers built to sense the world, make a decision in microseconds, and drive the right outputs—over and over, for years. Open one and you’ll find a tightly integrated mix of compute, memory, and I/O designed for predictability rather than spectacle. Program code lives in on-chip Flash or ROM, data in SRAM, and a web of peripherals (timers, PWMs, ADCs/DACs, UART/SPI/I²C, USB, CAN, Ethernet, and often radio blocks) orbit the core so tasks can run with minimal overhead. Families span humble 8-bit parts for simple chores to 32-bit Arm® Cortex-M and modern RISC-V MCUs with DSP and floating-point units for signal processing and control. Crucially, their interrupt architecture is tuned for deterministic behavior, keeping interrupt latency low so control loops stay stable and deadlines are met.

In practice, MCUs excel wherever energy and space are scarce but responsiveness is non-negotiable. A coin-cell wearable duty-cycles sensors, timestamps heartbeats, and secures a BLE link without ever warming your wrist. A brushless-DC motor drive samples phase currents via high-speed ADCs, runs a FOC algorithm on a cycle-counted schedule, then updates PWM registers—all inside a few dozen microseconds. Smart meters, thermostats, power supplies, appliance controllers, environmental sensors, and industrial nodes build on the same playbook: read → decide → act, with watchdogs, brown-out detection, and fail-safe boot to survive the real world.

What makes MCUs builder-friendly is the ecosystem. Vendors ship pin-compatible lines so you can scale flash size, RAM, or peripherals without respinning the PCB, and software compatibility means your drivers and middleware follow along. Toolchains (IDE + compiler + debugger), HALs, RTOS ports, and reference designs compress bring-up time, while low-power modes, DMA engines, and peripheral-to-peripheral triggers let you move data and keep clocks slow when nothing urgent is happening. Security has moved on-die as well: secure boot ROMs, hardware crypto, true random number generators, and key storage anchor encrypted updates and authenticated communications from day one.

You’ll see familiar names across the landscape: Texas Instruments, STMicroelectronics, Microchip Technology, NXP, Renesas, Infineon, Nordic, Silicon Labs, and Espressif (a favorite when Wi-Fi/BLE and aggressive BOMs matter). Each brings signature strengths—motor control libraries, ultra-low-power wireless, automotive-grade safety features, or cost-optimized connectivity—so selection often starts with your must-have peripherals and ends with lifecycle guarantees, community support, and total cost.

If you’re choosing an MCU, think like a systems engineer: define the control loop timing and worst-case CPU load, budget memory for stacks, buffers, and OTA slots, list the exact I/O (ADC resolution and sample rate, PWM channels, bus speeds), and profile power in real duty cycles. Get these right and an MCU will give you the best performance-per-watt in embedded computing—quietly running your product’s heartbeat long after the splashier parts have gone to sleep.

2) Digital Signal Controllers (DSCs)

Digital Signal Controllers sit in the sweet spot between classic microcontrollers and full-blown DSPs. Think of them as control engineers’ power tools: they run tight, deterministic control loops like an MCU, yet chew through math-heavy workloads—filters, transforms, estimators—with DSP-grade efficiency. Architecturally, a DSC marries real-time I/O, timers, and interrupts with single-cycle MAC units, wide accumulators, and specialized instructions that keep multiply-accumulate pipelines saturated while peripherals stream data in the background.

When your application must sense → compute → actuate in tens of microseconds, determinism and math throughput aren’t optional. DSCs are built for exactly that. Their instruction sets and addressing modes (circular buffers, bit-reversed access, saturation/rounding) make FIR/IIR filters, Park/Clarke transforms, PLLs, and modulators not just possible but efficient. Hardware-triggered ADC–DMA–PWM chains let you sample currents or voltages at precise electrical angles, run field-oriented control (FOC) or power factor correction (PFC), and update gate signals within the same control period—without wasting cycles on data shuffling. The result: rock-solid loops, higher efficiency, and quieter EMI signatures.

With a DSC, you trade general-purpose flexibility for precision, speed, and repeatability right where physics happens—at the motor phase, the inductor ripple, or the audio waveform. If your product’s differentiation lives in tighter control loops, cleaner waveforms, higher efficiency, or lower acoustic noise, a DSC gives you the right silicon muscles to get there.

3) Application-Specific Embedded Processors

Sometimes a plain MCU isn’t enough—you need silicon that can paint pixels, run neural nets, encrypt at line rate, and juggle multiple high-speed peripherals without breaking a sweat. Application-specific embedded processors are built for exactly that. They combine general-purpose control with targeted hardware that makes certain tasks astonishingly fast and power-efficient, turning “impossible on a battery” into “everyday.”

System-on-Chip (SoC): the Swiss-army brain

An SoC packs CPU cores (often heterogeneous), GPU/NPU blocks, high-bandwidth memory interfaces (DDR/LPPDR), and a freeway of high-speed I/O—MIPI CSI/DSI for cameras and displays, PCIe, USB, Ethernet—plus integrated radios (Wi-Fi/Bluetooth/Cellular) in many variants. This convergence enables rich UIs, real-time video pipelines, and always-connected experiences on a single package. Modern SoCs coordinate dozens of DMA engines and hardware schedulers so pixels, tensors, and packets flow with zero-copy handoffs while CPUs focus on orchestration, not shoveling data.

ASIPs: instruction sets with an opinion

Application-Specific Instruction-set Processors sharpen the compute knife even further. By tailoring the ISA—adding bit-manipulation, crypto primitives, custom vector ops, or fixed-function loops—ASIPs deliver deterministic throughput for narrow but performance-critical kernels: block ciphers, forward-error correction, image signal processing, or SLAM building blocks. The payoff is dramatic: lower latency, smaller code size, and fewer watts per operation, often with compile-time toolchains that map high-level code directly onto those bespoke instructions.

Application-specific processors give you bespoke speed where it counts—vision, AI, crypto, high-speed I/O—while keeping the rest of the system flexible. If your product lives or dies on frame time, inference latency, or packets per watt, this is the class of silicon that turns ambitious requirements into shippable hardware.

4) Real-Time Processors

Real-time processors are built for one promise above all others: when the world asks a question, they answer on time—every time. Instead of chasing peak benchmarks, they are engineered for determinism: bounded interrupt latency, jitter you can budget, and schedulers that preempt exactly when you tell them to. Paired with a Real-Time Operating System (RTOS), an RTP gives you priority-based preemption, fixed-tick or tickless scheduling, and IPC primitives that behave predictably under stress. The result is software you can reason about with a stopwatch, not just a profiler.

With a real-time processor, you don’t merely run fast—you run on schedule. That reliability lets control loops stay stable, actuators remain tame, and auditors stay happy. In systems where milliseconds separate safe from unsafe, RTPs and RTOSes give you the only metric that matters: guaranteed timing, by design.

Architecture: What’s Inside a Typical Embedded System

An embedded device is a tight choreography of hardware blocks and software layers, all tuned to meet deadlines, sip power, and survive real-world noise. Think of it as a small city: a core that makes decisions, roads (buses/interconnects) that move data, utilities (power and clocks) that keep everything running, and services (drivers, RTOS, middleware) that deliver functionality without breaking determinism.

Core elements

Processor/Core

Typically Arm® Cortex-M/A/R, RISC-V, or a proprietary real-time core. Beyond ISA, what matters is the execution model: interrupt latency, presence of FPU/DSP extensions, lockstep options for safety, and access to tightly coupled memory (TCM) for jitter-free code and data.

Interconnect & DMA

AXI/AHB/APB fabrics (or vendor equivalents) connect cores, memory, and peripherals. A capable DMA engine (with scatter-gather and linked lists) lets sensors stream into RAM while the CPU sleeps. QoS and bus arbitration settings are critical when ADCs, radios, and display engines contend for bandwidth.

Memory hierarchy

- Nonvolatile: on-chip Flash/ROM for boot and firmware images (often with ECC and dual-bank for safe OTA).

- SRAM/TCM: deterministic access for ISRs/control loops; cacheable SRAM for bulk buffers.

- External: SDRAM/PSRAM/DDR for framebuffers, ML tensors, and file caches—fast but power-hungry and less deterministic; lock or bypass caches for real-time paths.

Clocking & Reset

Multiple oscillators (HSE/LSE/HSI), PLLs for performance bursts, and independent watchdog clock domains. Brown-out detection, clock failure detection, and nuanced reset trees (POR, system, peripheral) prevent latent faults.

Peripherals

Timers/PWM with dead-time insertion, ADC/DAC with hardware triggers, GPIO with interrupt-on-change, serial (UART/SPI/I²C), USB, CAN/LIN, Ethernet, SDIO, camera/display (MIPI CSI/DSI, parallel RGB), and often RF blocks (BLE/Wi-Fi). For control systems, the ability to synchronize ADC sampling to PWM edges is gold.

Power Management

Regulators and power domains define “always-on,” “retention,” and “switchable” islands. Voltage monitors, battery gauges, and load switches support graceful degrade. Hardware assists—like autonomous low-power peripherals—let the chip do useful work while the core sleeps.

Software stack

- Bare metal or RTOS (FreeRTOS, Zephyr, ThreadX, embOS, SafeRTOS) depending on timing complexity.

- Middleware: TCP/IP, TLS, USB, filesystems, BLE/Matter, OTA, diagnostics.

- Application: C/C++ dominates, with growing Rust for memory safety in drivers and critical logic.

- Tooling (IDE, build system, unit tests, CI) and logging/tracing (ITM/SWO, ETM, SEGGER RTT) are first-class to prove timing and debug rare field issues.

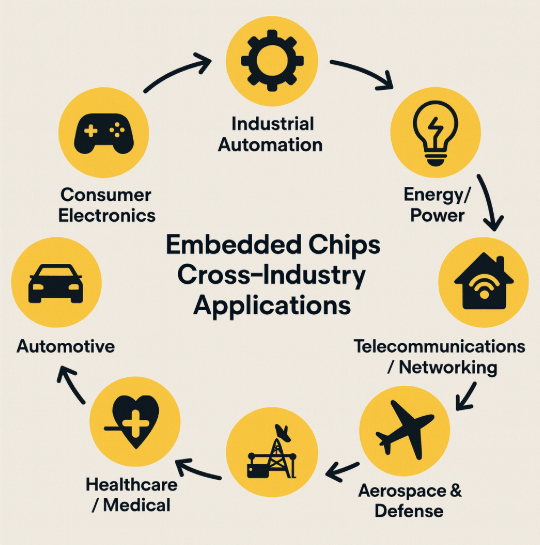

Embedded Chips Cross-Industry Applications

Consumer Electronics

Smart thermostats, wearables, e-readers, and smart speakers rely on MCUs/SoCs for sensor interfacing, UI control, wireless stacks, and power management. Key metrics: wake-up latency, always-listening current, and secure OTA.

Automotive

Control units manage engines, thermal systems, BMS for EVs, infotainment, and ADAS sensor fusion. Requirements include temperature range (–40 to +125 °C), EMC robustness, functional safety (ISO 26262), and long lifecycles.

Industrial Automation

PLCs, drives, and industrial sensors leverage MCUs/DSCs for closed-loop control and real-time comms (EtherCAT, PROFINET, CANopen). Local inference reduces cloud dependence and latency—core to Industry 4.0.

Healthcare & Medical

From wearable ECGs to infusion pumps, systems demand low power, traceability, risk management, and compliance with standards (e.g., IEC 60601 for safety, ISO 14971 for risk).

Aerospace & Defense

Radiation-tolerant parts, redundancy, and rigorous verification dominate. Determinism and fault containment are paramount, with hardware and software certified under stringent processes.

Embedded vs. General-Purpose CPUs: A Quick Contrast

Choosing between an embedded processor and a general-purpose CPU isn’t just about speed—it’s about the constraints your product must live within: power budget, latency guarantees, integration level, lifetime supply, and total cost. The matrix below highlights how these architectures trade off in real projects, from battery wearables to factory gateways.

| Aspect | Embedded Processors | General-Purpose CPUs |

| Function | Task-specific control loops and fixed workflows | Versatile, multi-application compute (desktop/server paradigms) |

| Power | Very low; optimized sleep states and 碌A standby | Higher baseline draw; idle often watts not 碌A |

| Integration | Peripherals on-chip (ADC/DAC, PWM, CAN, BLE) | Relies on external chipsets and add-in controllers |

| Real-time | Deterministic with RTOS; bounded ISR latency | Limited determinism; preemption and jitter typical |

| Cost | Optimized BOM; small PCB, fewer parts | Higher silicon/platform cost; larger boards |

| Memory Footprint | Small (KB鈥揗B); on-chip Flash/SRAM common | Large (GB); external DRAM/SSD expected |

| Thermals/Form Factor | Fanless by design; QFN/BGA, WLP packages | Often needs heatsinks/fans; larger mechanical envelope |

| I/O Latency | Microsecond-class GPIO/PWM response | Millisecond-class under OS load unless tuned |

| OS & Software | Bare-metal/RTOS, tight control of timing | Full OS (Linux/Windows); rich user space, drivers |

| Security Model | Secure boot, trust anchors on-die, fixed lifecycle | Broad features (TPM/TEE) but larger attack surface |

| Lifecycle & Supply | Long availability (industrial/auto SKUs) | Faster churn; consumer/server lifecycles |

| Scalability | Scale by adding MCUs/DSCs per function | Scale up with cores/threads/accelerators |

| Performance/ Watt | Excellent for control and signal tasks | Excellent for throughput and mixed workloads |

| Upgrade Path | Pin-compatible families; incremental | Big jumps tied to sockets/chipsets/platforms |

If your must-haves include battery life, hard real-time response, tiny PCBs, and predictable unit cost, favor embedded (MCUs/DSCs/real-time processors). You’ll ship sooner with fewer parts, simpler thermals, and deterministic behavior.

If your problem leans on rich OS services, heavy networking, containers, large ML models, or complex UIs, a general-purpose CPU (or SoC) pays off—accepting more power and thermal headroom in exchange for developer velocity and ecosystem breadth.

Many successful products blend both: an MCU handles time-critical control while a Linux-class CPU tackles UI, analytics, and connectivity. This split architecture keeps safety-critical loops deterministic while letting higher layers evolve quickly.

Bottom line: embedded wins whenever edge constraints—power, latency, integration, and cost—dominate throughput needs. Reach for general-purpose CPUs when your primary bottleneck is software complexity, feature velocity, or raw application throughput rather than hard real-time control.

Conclusion

Embedded processors and controllers are the invisible infrastructure of modern life. Their mandate is demanding: react now, consume almost nothing, never fail, stay secure, and last for years. Choosing the right silicon, architecting for determinism and power, and building in security and updateability from day one are what separate a demo from a durable product.

Whether you’re spinning a motor at 20 kHz, streaming sensor data over BLE on a coin cell, or running a vision model at the edge, the playbook is consistent: clarify requirements, design for constraints, measure ruthlessly, and iterate. Master that cycle, and you’ll build systems that quietly run the world—one control loop, one packet, and one perfectly timed interrupt at a time.