Flip Flop Timing Diagram: Setup Time, Hold time and Propagation Delay

- Setup Time (Tsu): The minimum time the data input (D) must be stable before the active edge of the clock for the flip-flop to reliably capture the data.

- Hold Time (Th): The minimum time the data input (D) must remain stable after the active edge of the clock for the flip-flop to reliably capture the data.

- Propagation Delay (Tpd): The time it takes for the output (Q) of the flip-flop to change state after the active edge of the clock.

Explanation

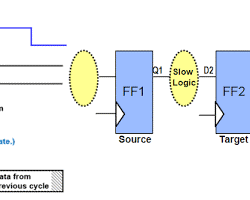

The timing diagram illustrates the relationship between the clock signal, data input (D), and output (Q) of a flip-flop.

- Setup Time:

- The data input (D) must be stable for a period of Tsu before the rising edge of the clock.

- If the data changes after the setup time but before the clock edge, the flip-flop’s output might be unpredictable.

- Hold Time:

- The data input (D) must remain stable for a period of Th after the rising edge of the clock.

- If the data changes before the hold time expires, the flip-flop’s output might be unpredictable.

- Propagation Delay:

- The output (Q) changes state after a delay of Tpd from the rising edge of the clock.

- This delay limits the maximum clock frequency of the circuit.

Importance of Timing Parameters

- Setup and Hold Times: These parameters are critical for ensuring data integrity and preventing metastable states.

- Propagation Delay: This parameter determines the maximum operating frequency of the circuit. If the data path through multiple flip-flops takes longer than one clock cycle, the circuit will not function correctly.

Consequences of Violating Timing Parameters

- Setup Time Violation: The flip-flop might capture incorrect data, leading to unpredictable behavior.

- Hold Time Violation: The flip-flop might enter a metastable state, where the output is indeterminate for an indefinite period.

- Propagation Delay Violation: The circuit might not operate at the desired speed or might malfunction.

Designing with Flip-Flops

To ensure correct operation of a digital circuit, it is essential to:

- Choose flip-flops with suitable timing parameters for the desired operating frequency.

- Carefully analyze the data paths to meet setup and hold time requirements.

- Use appropriate clock distribution techniques to minimize clock skew.