RISC based CPU Designing in the Reversible Logic Scheme

In this article, I have discussed about how to design RISC based CPU in reversible logic scheme? With expanding scaling down of incorporated circuits, the decrease of force dispersal has become a critical issue in the present equipment configuration measure. While because of high mix thickness and new creation measures, energy misfortune has essentially been diminished throughout the most recent many years, actual cutoff points brought about via Landauer’s rule will remain. Landauer saw that freely from the applied innovation ln 2·kT Joule of energy is disseminated for each lost piece of data (k is the Boltzmann steady and T is the temperature). That is, each time for example an AND activity is performed, where two input esteems are changed into a solitary one, this small amount of energy is dispersed. While this sum has been irrelevant previously, specifically for future plans it turns into an progressively significant factor.

To stay away from this actual impediment, specialists propose reversible circuits as a promising other option. Effectively in the 1970s, Bennett showed that zero energy scattering is as it were conceivable, if data lossless calculation is performed. This applies to reversible circuits, since they map each information design exceptionally to a specific yield design. First physical acknowledge affirming this perception (for example as far as a reversible CMOS 4-digit viper) have effectively been introduced. RISC based CPU designing in reversible logic scheme.

Driven by these outcomes just as by further encouraging applications (for example in the area of quantum calculation), specialists began to apply these ideas on bigger hardware. Central Processing Units (CPUs) – as the center component of numerous frameworks – got consequently specific consideration. Nonetheless, either hand-made models or preparing units with an exceptionally little arrangement of upheld activities have been introduced up until now.

It is safe to say that you are From Pakistan? Undertaking Management Jobs May Pay More Than You Think. Online Project Management Courses | Search advertisements

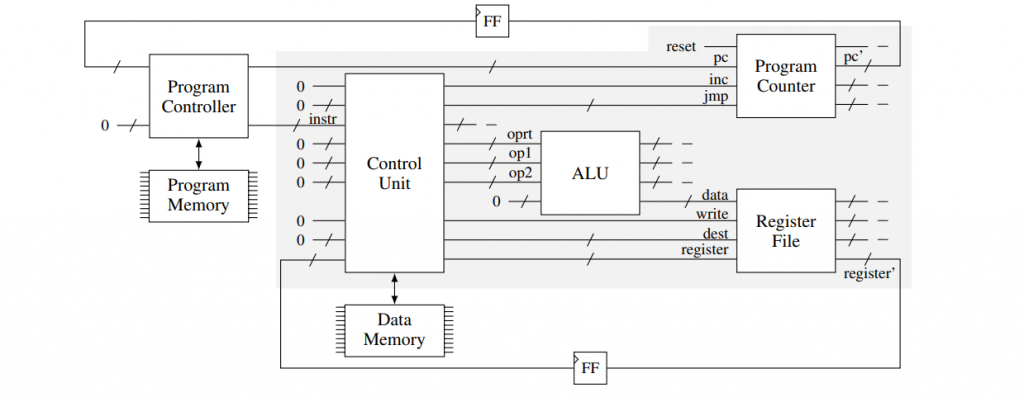

In this article, the new advancement in the field of reversible circuit configuration is utilized to plan an unpredictable framework, for example a RISC CPU made out of reversible doors. Beginning from a printed particular, first the center segments of the CPU are distinguished. Recently presented approaches are applied close to understand the individual combinational and consecutive components. All the more correctly, the combinational parts are planned utilizing the reversible equipment depiction language SyReC , though for the acknowledgment of the consecutive components an outside regulator.

Parts of CPU

Stopping the separate parts together, a CPU plan results which can deal with programming programs written in an constructing agent language. This is shown for a situation study, where the execution of a program deciding Fibonacci numbers is reproduced. Therewith, the commitment of the paper is twofold. On the one hand, a complete contextual analysis is given, appearing the utilization of best in class plan methods all together to plan an enormous framework. Taking into account that a few years prior, programmed blend approaches were appropriate to capacities given as far as truth-tables just , this is a significant venture towards the plan of top of the line frameworks in reversible rationale.

Then again, with the subsequent reversible CPU, a nontrivial reversible circuit opens up, which can fill in as benchmark for different regions like check or test1.

Reversible Logic Design

To acknowledge combinational reversible circuits, a wide scope of amalgamation approaches have been presented in the late years (see for example. The majority of them depend on Boolean portrayals, for example, truth tables or Binary Choice Diagrams (BDDs). Be that as it may, since the CPU incorporates complex activities (for example enormous control ways and math tasks), we utilized the SyReC programming language also as its particular amalgamation motor to understand the combinational segments of the CPU [17]. Hence, the control unit, the ALU, and the program counter can be executed on a more elevated level of deliberation.

This maintains a strategic distance from versatility issues, which would happen if truth-table based or BDD-based methodologies were applied. Conversely, progressive combination draws near (like the SyReC motor) will in general produce circuits with countless consistent inputs. This can somewhat be improved by post-union streamlining approaches , yet at the same time stays an open issue, which is left for future work. Other than that, new plan standards must be thought of.

One new plan worldview becomes effectively apparent in this model. As indicated by the determination, the program counter ought to be appointed 0, if the essential input reset is appointed 1. Because of an absence of ordinary task activities which would annihilate the reversibility, this is acknowledged by another extra sign (signified by nothing what’s more, set to 0) just as a SWAP activity. Comparable plan choices must be made for example to understand the ideal control way or to execute the separate. Usefulness of the ALU. Conversely, the expansion of the program counter is a reversible activity and, in this manner, can without much of a stretch be carried out by the individual += guidance (Line 9).

The subsequent circuit created by the SyReC synthesizer is appeared. Note that the piece widths of the signs are downsized to 2 to improve the meaningfulness. The initial two lines give the current worth of the program counter (pc_1, pc_0), while similar lines on the right-hand side hold the following state esteems (pc_10 , pc_00 ) utilized as contributions for the flip-flops as portrayed.

The leftover combinational segments are acknowledged correspondingly. Be that as it may, because of page impediment and size limitations, the complete SyReC code just as the subsequent circuits of all combinational segments can’t be given in this paper. The sources are totally accessible on RevLib. C. Successive Components While for the blend of combinational reversible circuits, countless methodologies has been presented, research on plan answers for consecutive segments is simply toward the start. Two unique ideal models are as of now under definite thought. The principal worldview (recommended for example in [16]) contentions that a reversible circuit holds in its state as long as its sign values stay unaltered. In this way, a combinational circuit can be treated as a center part of a successive gadget.

More exactly, utilizing for example an old style (non-reversible) regulator, yield esteems from one cycle are applied to the individual input signs of the following cycle. Consequently, the timing as well as the input is dealt with by the regulator, while the real calculation is performed on a combinational reversible circuit.

The subsequent worldview considers the acknowledgment of the consecutive components straightforwardly in reversible rationale. For this reason, a few ideas on the most proficient method to understand the particular memory components as flip-flounders, hooks, or registers have been made. Utilizing these fundamental successive components, more perplexing consecutive parts can undoubtedly be built.

Also read here for more detail

https://science.jrank.org/programming/CPU_Design.html

https://eevibes.com/hardware-devices/cpus/how-to-measure-a-cpu-performance/